As large model training clusters scale from thousands of GPUs to hundreds of thousands, and one second of GPU idling equates to the cost of a Tesla, the network is no longer merely a “pipeline” but the “third productivity” alongside computing power and storage. Consequently, the 400G Ethernet switch has become the sharpest focal point of data center capital expenditure in 2025: on one side, the triple extreme of bandwidth, latency and packet loss driven by AI workloads; on the other, the financial red line of cost reduction and efficiency improvement for cloud vendors. Whoever can build the 400G switch into an AI-native device will seize the pricing power in the next round of cloud competition. This 3,000-word report dissects the global 400G switch market pattern, technology stack restructuring, ecological reshuffle and roadmap, answering a core question: how exactly is AI reinventing the “switch”.

400G Ports Become the Mainstream, 800G Scales Up in Succession

According to Q3 2025 data from IDC, the global Ethernet switch market generated $14.7 billion in revenue, a year-on-year increase of 35.2%, with the data center segment surging 62% year-on-year. The penetration rate of 400G ports exceeded 38% for the first time, establishing itself as the de facto primary speed standard. Dell’Oro forecasts that by 2027, 400G+800G ports will collectively account for over 40% of data center ports; Crehan takes a more aggressive view, predicting that 800G port shipments will surpass 20 million in four years, with corresponding revenue surging 91.6% quarter-on-quarter in 2025 and already accounting for 18.3% of data center switch revenue.

Geographically, North American cloud giants (AWS, Azure, Meta) completed full 400G deployment in 2025 and will launch large-scale 800G rollout in 2026. In the Chinese market, the data center switch market reached RMB 21.15 billion in 2024 and is projected to hit RMB 22.68 billion in 2025, with AI computing networks contributing over 45% of the growth. The procurement share of 400G ports among leading Chinese cloud vendors has risen from 35% in 2024 to more than 50% in 2025.

In terms of volume and price, the unit price of high-end 400G/800G models has increased by 18%-22%, offsetting the downward pressure from white-boxization and driving the overall market average selling price (ASP) to maintain a high single-digit growth. In short: 400G is the current cash cow, 800G is the second growth curve for the next two years, and 1.6T is lined up for commercial launch in 2026.

AI Backend Networks Spur a New Topology

The traditional three-tier Spine-Leaf architecture is designed for north-south business traffic; AI training brings bursty east-west All-Reduce traffic, stretching the network architecture into a dual-plane of front-end + back-end:

The front-end adopts 25.6T box-type switches, with 100G/400G downlink to GPU computing nodes;

The back-end uses 51.2T box-type switches or modular chassis, with 800G uplink for storage and gradient synchronization, featuring a latency budget of <2 µs and packet loss <10⁻⁶.

Actual tests on OpenAI’s 10,000-GPU cluster show that for every 1 µs increase in network jitter, GPU utilization drops by 0.6%, corresponding to tens of millions of dollars in computing power waste. For this reason, cloud vendors have included network hours alongside GPU hours in their service level agreements (SLAs), elevating 400G/800G switches from a cost center to a profit center.

51.2T Chips, 112G SerDes and CPO Advance in Tandem

Chip Layer

Broadcom’s Tomahawk 5 (51.2T) entered mass production in Q2 2024, adopting 112G PAM4 SerDes with a single-chip power consumption of 385 W; Marvell’s Teralynx 10 and NVIDIA’s Spectrum-4 followed closely. In 2025, the industry began sampling 102.4T chips, with 1.6T ports per slot ready for commercialization, paving the way for 1.6T Ethernet.

Packaging Layer

A 51.2T chip requires more than 512 SerDes lanes, and traditional pluggable modules have hit a bottleneck in power consumption and heat dissipation, making Co-Packaged Optics (CPO) a necessity. Broadcom launched the Bali platform in 2025, co-packaging optics with switch chips, reducing power consumption by 30% and doubling density; NVIDIA’s CPO version of Quantum-X/Spectrum-X will be launched in 2026, sharing the cooling air duct with the GPU backplane and cutting the overall cabinet power consumption of AI clusters by 7%.

Algorithm Layer

The Ultra Ethernet Consortium (UEC) released the “AI Transport” draft in 2024, introducing multi-path, selective retransmission and RTT-aware congestion control at the Ethernet MAC layer, compressing the AI training flow completion time (JCT) to within 1.2 times that of InfiniBand. With more than 60 ecological vendors participating, Ethernet has thus obtained the entry ticket to the AI backend network.

Accelerated White-boxization, Re-centralization of Hardware-software Integration

ODM direct sales revenue soared 152.4% year-on-year in Q3 2025, accounting for 30.2% of data center switch revenue and exceeding 30% for the first time. Cloud vendors develop their own OS (SONiC derivatives) paired with white-box hardware, decoupling software subscription fees from hardware sales and boosting gross profit margins by 8-10 percentage points.

However, the chip side is witnessing anti-white-boxization: the barriers for 112G/224G SerDes, 3 nm process and 2.5D Interposer have risen sharply, with the R&D cost of a single chip exceeding $300 million. Only three players—Broadcom, Marvell and NVIDIA—can afford the investment. Conclusion: hardware is converging while software is diverging. A new buyer-seller relationship has formed between software-defined cloud vendors and chip-defined semiconductor giants, with traditional branded switch vendors caught in the middle and their market share being continuously squeezed.

Three-tier Hierarchy Solidified

First Tier: Broadcom (>55% market share), Marvell (20%), NVIDIA (12%)—controlling the pace of 112G/224G SerDes and CPO technology;

Second Tier: Cisco, Arista, H3C—holding onto the high-end government and enterprise market with proprietary OS and existing customers;

Third Tier: Centec, H3C Semiconductor, Unisoc—having just mass-produced 112G SerDes, focusing on domestic substitution and independent innovation.

The market share of domestic switch chips in China is expected to reach 18% in 2025, with a target of 30% by 2027, but production capacity and IP cores remain key bottlenecks.

Liquid Cooling Shifts from “Optional” to “Mandatory”

A 51.2T box-type switch has a power consumption of over 700 W, with a 1U surface power density of 6000 W·m⁻², breaking the limit of air cooling. Meta will adopt cold plate liquid cooling for 100% of its new AI clusters in 2025; China’s East Data West Computing hubs require a PUE of <1.15, making liquid cooling a bidding threshold for 400G/800G switches. From the industrial chain perspective, liquid cooling quick connectors, CDUs and optical cold plates have been unified to the OCP Open Cooling standard in 2025, with costs falling 22% year-on-year, paving the way for large-scale deployment.

Conclusion

AI large models have transformed the “network” from a cost item into an independent variable of the computing power function: doubling bandwidth, halving latency and approaching zero packet loss have become the life-and-death line for achieving GPU utilization of over 90%. As a result, the 400G Ethernet switch has broken away from the traditional “bandwidth race” and evolved into an AI-native computing power scheduler—it is no longer just a hardware box, but a systemic innovation integrating chips, algorithms, optoelectronic devices, liquid cooling and software ecology. Whoever can first turn 51.2T chips, CPO, UEC protocols and liquid cooling cabinets into a turnkey solution will replicate the “profiteering curve” of 100G in the 2026 800G window. The story of the switch has only just entered the AI era with the advent of 400G.

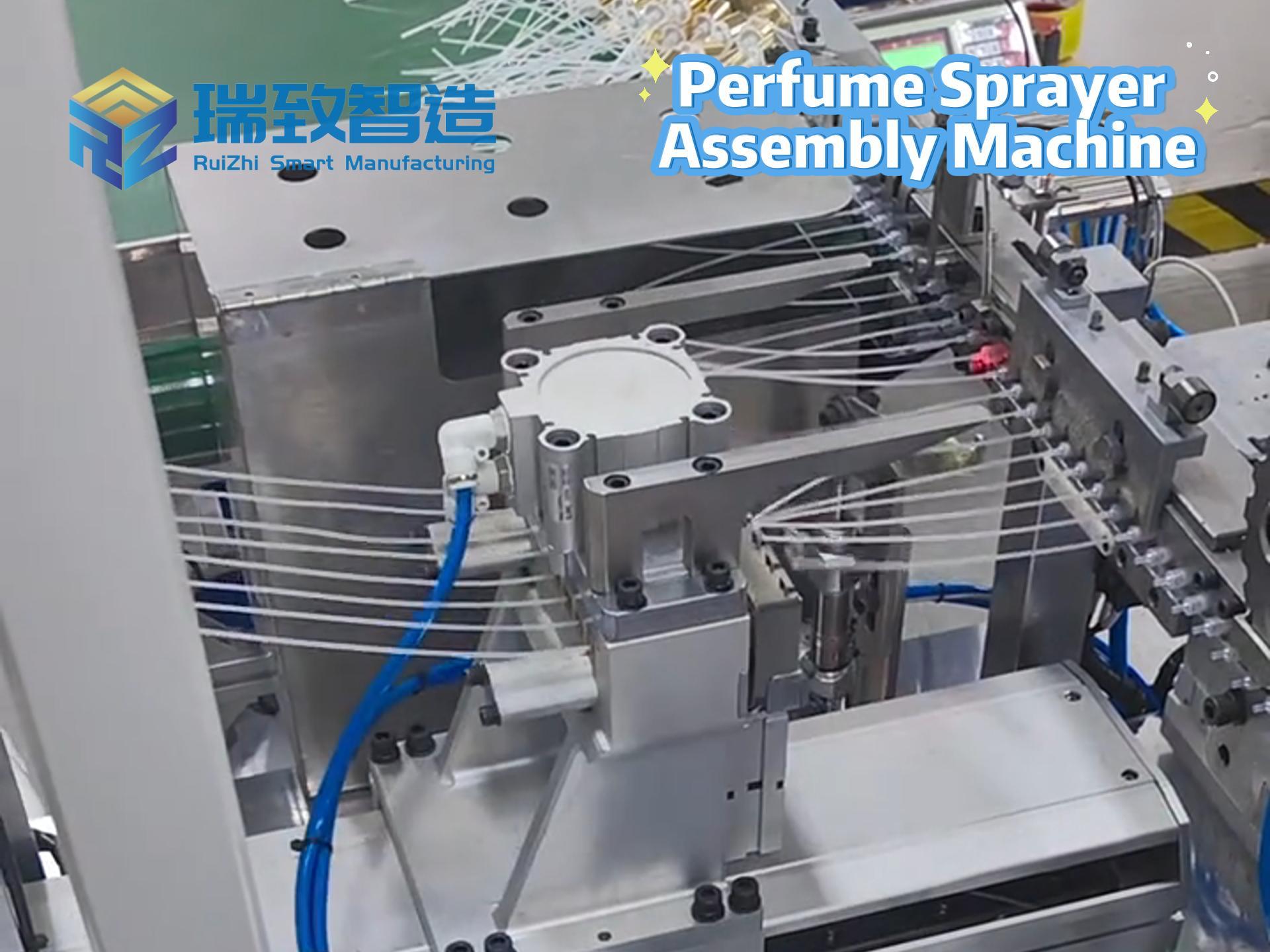

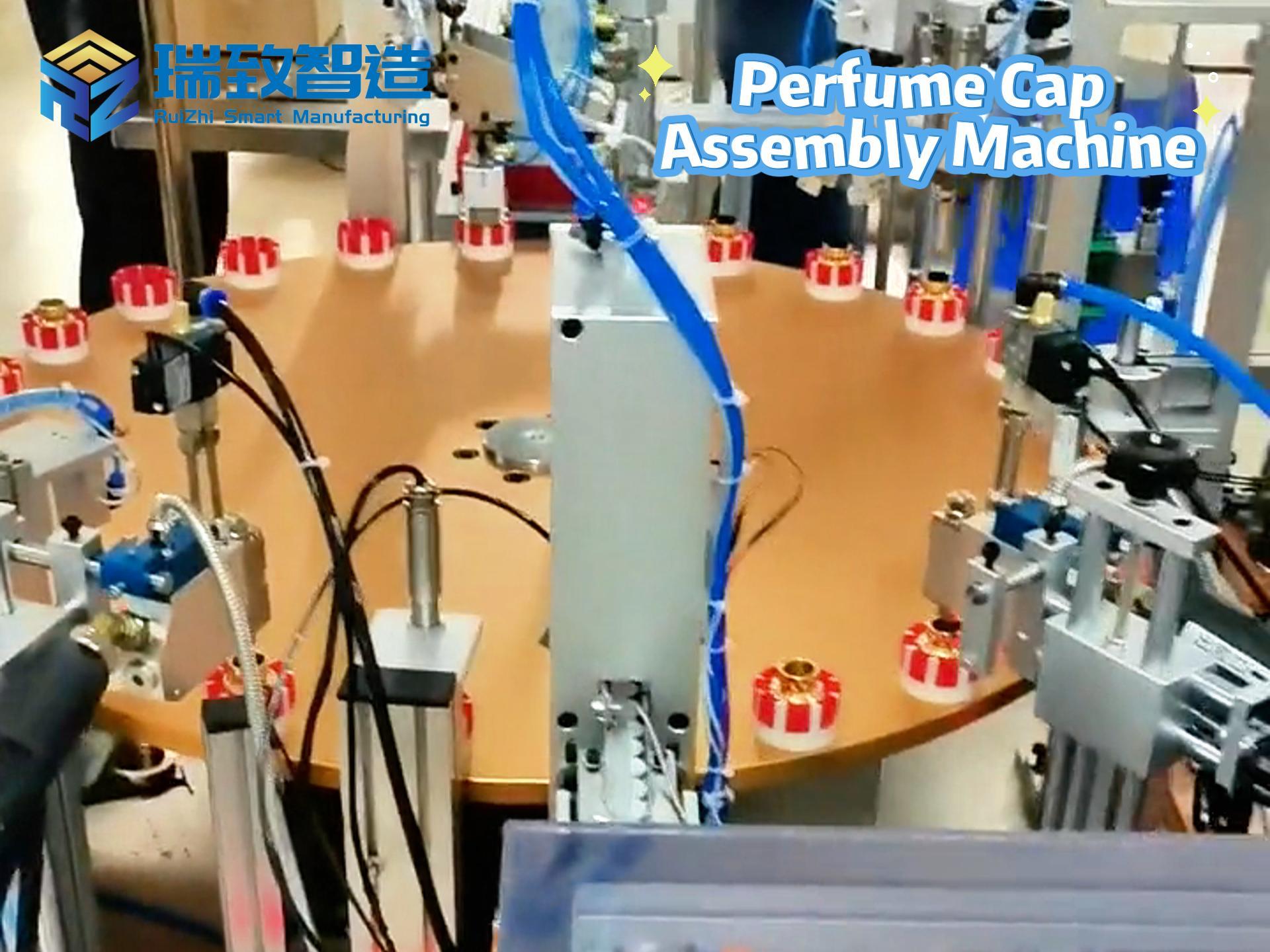

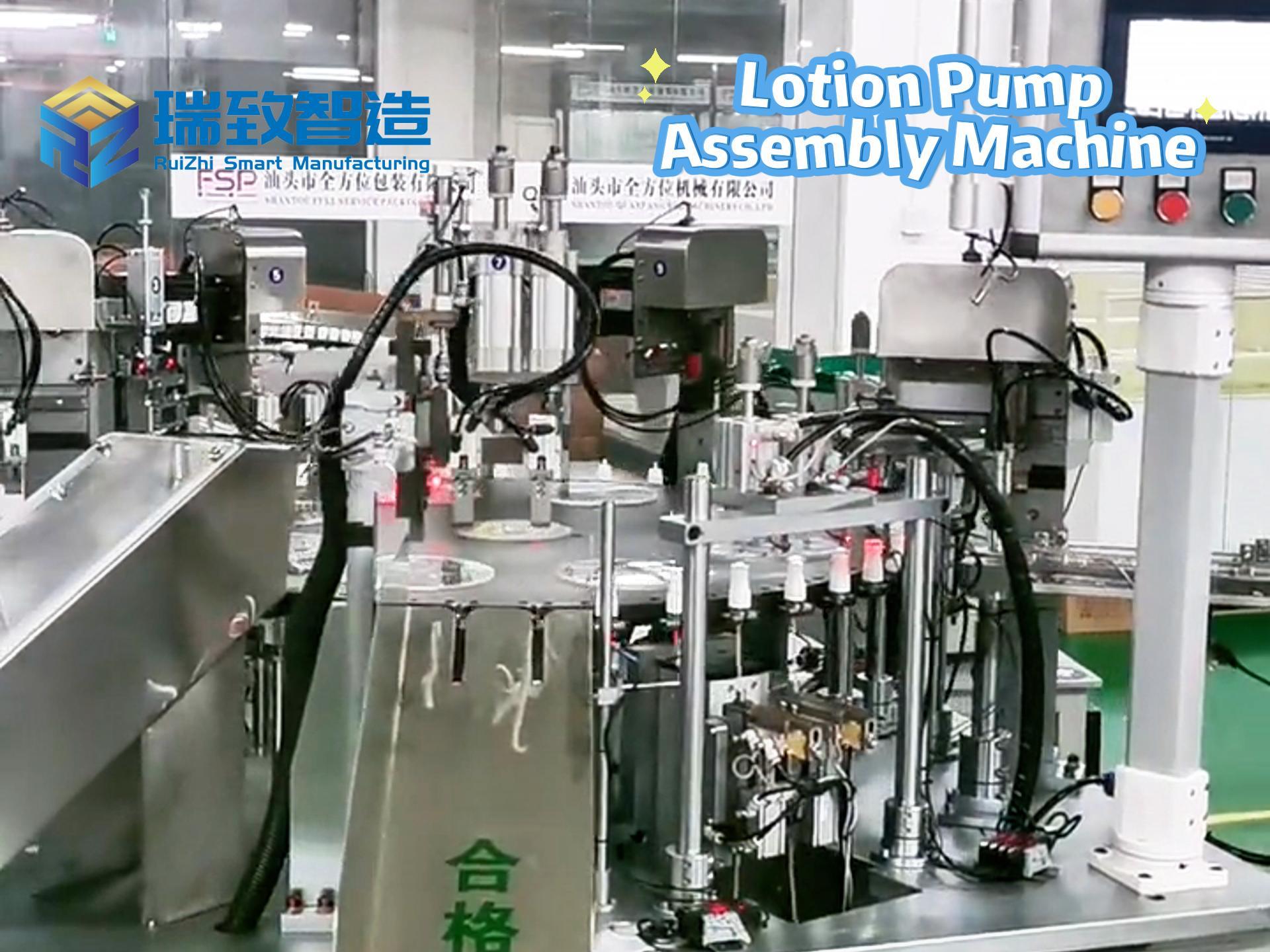

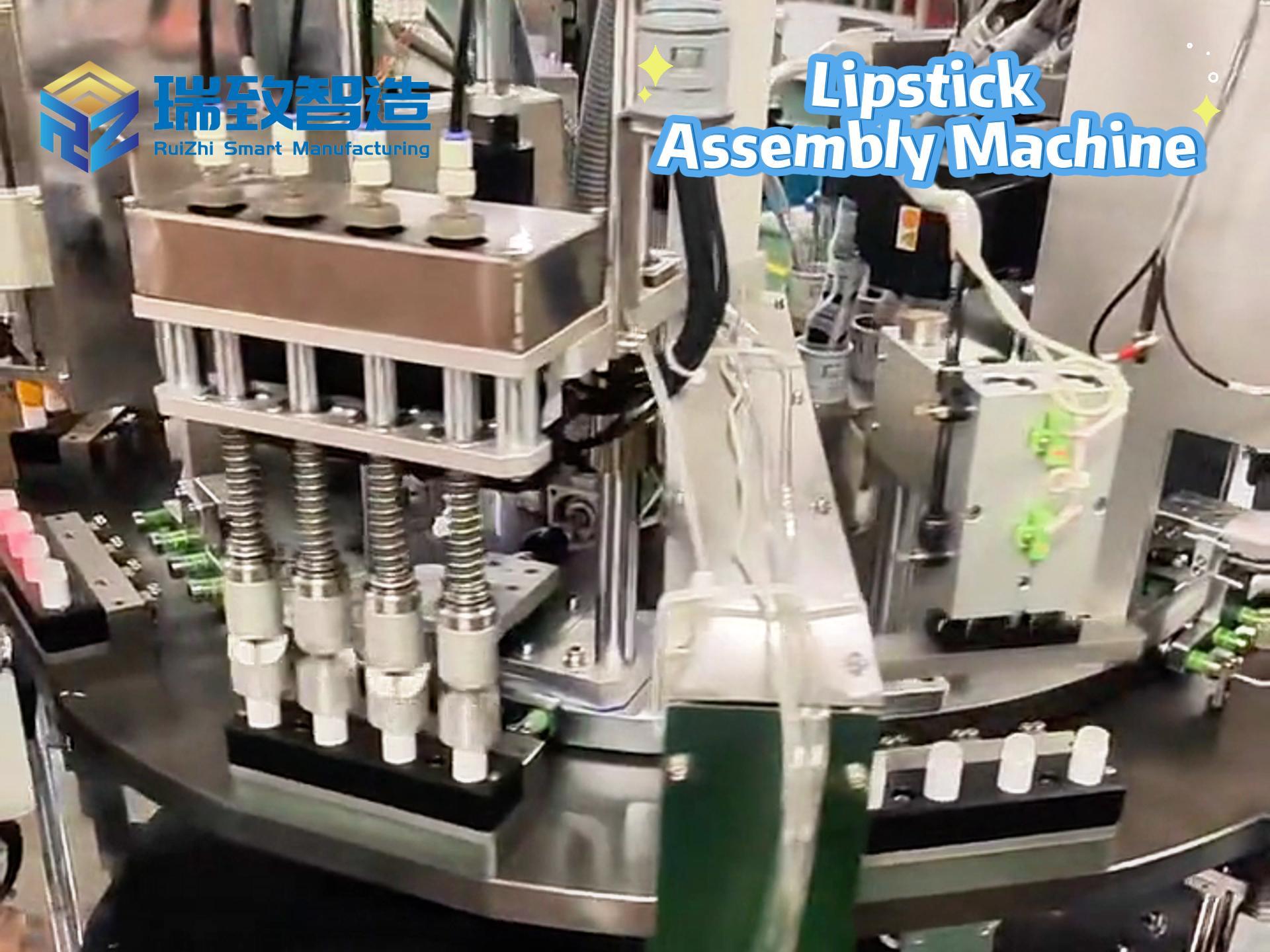

Automation engineering of production lines in the automotive industry

AI production line automation robots in the automotive industry